SIP

Материал из Wiki.

SIP (Serial Initialization Packet) - протокол инициализации процессора в AMD K7-системах. Северный мост посылает серию таких "пакетов" процессору сразу же после старта системы. Посредством этого протокола задаются характеристики шины EV6.

Для описания подробностей можно использовать разбор принципов работы КУ на форуме ixbt. Могу сказать, что после прочтения "заветного" когда-то "закрытого" даташита "AMD Athlon™ System Bus Specification" могу где-то даже "загордиться" собой - все предположении о механизме работы, в том числе даже диаграммы сигналов - один к одному из оного. :)

Несмотря на кажущуюся избитость темы, всё не так просто. Интересует не вопрос "Как изменить коэффициент умножения?", а "Как он РАБОТАЕТ?". Инфы по изменению - беспросветная тьма, но вся она представляет собой лишь "эмпирические" данные без какой бы то ни было "теоретической" базы. А в случае возникновения "непонятных" ситуаций, например, популярная проблема того же незапуска тех же Tbred-ов на не самых новых матерях, вообще часто похожа на плоды труда пионеров, выявивших зависимость слуха тараканов от количества оставшихся у них ног. Поэтому хотелось бы собрать по крупицам имеющуюся информацию и попытаться увидеть ситуацию в анфас (а не плохой снимок ботинка правой ноги).

«Главные» СИГНАЛЫ (для установки КУ):

- сигналы FID (Frequency ID) – подаются на NB (северный мост), который использует их для посылки процессору SIP-пакета (Serial Initialization Packet)

- сигналы BP_FID – недокументированные в официальных доках выводы, непосредственно влияющие на установку КУ посредством задачи оного с помощью так называемой «резисторной» логики (всем известные * «мостики»). Возможность влияния BP_FID на КУ имеется лишь при условии замкнутости мостиков L1.

ДОКИ: если бы у меня был доступ к AMD Athlon™ and AMD Duron™ System Bus Specification, order# 21902, я б не создавал эту тему. :)

Содержание |

Условия для корректной инициализации AMD K7

Вот, что можно почерпнуть из официальных доков – инициализация AMD K7 CPUs:

1. AMD говорит, что для корректной установки КУ, Reset должен подаваться до сигнала PowerOK, как минимум за 10nS. Это условие всегда выполняется – SB (южный мост) выставляет PowerOK спустя многие mS, а не nS.

2. К приходу PowerOK все напряжения уже должны установится в номинальные значения. Это условие всегда выполняется – для этого, собственно, и есть PowerOK.

3. Генератор к приходу PowerOK уже должен вовсю генерить нужную частоту. Далее в доках следует исключительно информативное предложение (одно!) по этой принципиальной теме:

- When PWROK is asserted, the processor switches from driving the internal processor clock grid from the ring oscillator to driving from the PLL.

Вот так всё просто – с приходом PowerOK процессор переключается с внутреннего на внешнее тактирование. Ни больше, ни меньше.

4. Промежуток от начала PowerOK до снятия Reset должен быть не менее 1mS, дабы дать время процессору «засинхронизироваться» в процессе переключения с внешнего на внутренее тактирование. Это условия всегда выполняется – SB обычно «перевыполняет» его как минимум в 1.5-2 раза.

5. PowerOK должен быть стабильным в процессе всей работы компьютера (иначе процессор опять станет переключаться между внутренним и внешним тактированиями, что, конечно, ничего хорошего не сделает).

6. NB_RESET# должен быть выставлен (в таком случае выставляется и CONNECT) до снятия Reset#. Это условия всегда выполняется. Если NB_RESET# не будет выставлен до окончания Reset, то подача CONNECT будет расценена процессором как начало передачи SIP-пакета. К сожалению, этот важный пункт совсем не отражён в доках, на диаграмме отстутсвуют главные инициализационные сигналы – PROCRDY, CONNECT, CLKFWDRST…

7. Чипсет должен считывать FID-ы не ранее чем через 100nS после PowerOK. Это условие появилось с выходом Palomino (аналогично – в Tbred/Barton). Просто в Tbird/Spitfire значения FID брались с мостиков L6 и там, понятно, никакого времени на стабилизацию не нужно. А в паломинах эти мостики исчезли их значение «генерится» самим процессором, на что и требуется некоторое время, дабы избежать считывания «не до конца» (неправильно) установившихся значений. Эта трансформация аналогична той, что произошла с VID/BSEL при «переходе» Coppermine-Tualatin. Выполняется ли это условие для чипсетов, «незнающих» паломинообразных процессоров – сказать сложно, это надо проверять. Если сравнить с установкой туалатинов на i440BX («аналогичная» проблема – в i815B0/Tualatin присутствует «задержка» считывания, а в i440BX – её нет) – то выполнением/невыполнением можно пренебречь.

8. После WarmReset-а опять же, требуется время на установку FID (см. п.7).

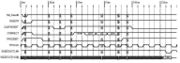

9. (Дорисовано мной) – после ресета следует передача SIP. Для этого используются сигналы PROCRDY/CONNECT/CLKFWDRST синхронизируемые по SYSCLK.

Инфы откровенно мало, понять что-либо невозможно. И вообще, сказать, что документации на AMD K7 немного - это ничего не сказать. Достаточно взглянуть на количество страниц доков (по сравнению с Intel) и всё становится ясно. Поэтому, чтоб найти хоть какую-то другую инфу, я пошёл другим путём – посмотрел, как это делается в Alpha 21264/EV6. Как известно, AMD лицензировала шину EV6 у DEC/Compaq, а документации на альфу существенно больше. ИМХО, из "единообразия" шины можно сделать и выводы по инициализации процессора, в т.ч. установке КУ. В пользу "единообразия" инициализации AMD K7 и Alpha 21264 говорит также и тот факт, что существуют даже платы конкретно под альфу на чипсетах AMD 750/760.

Инициализация AMD K7 на примере Alpha21264

В любом случае, хотя б попытаюсь «спроецировать» инициализацию Alpha21264 на AMD K7.

Инициализация (на примере Alpha 21264):

1-2. "Установка" и "сохранение" значений с линий FID. (для альфы это - мультиплексированные линии IRQ).

3. С подачей сигнала PowerOK (у альфы он обзывается DCOK) "снятые" значения FID устанавливают коэффициент умножения. Сейчас пока внутренний генератор работает на частоте FSB/16, через 8 тактов она начинает "умножаться".

4. "Умножение" (до значения коэффициента) происходит в пять этапов. Каждый этап занимает Koef_max*Koef_max тактов. Для альфы это 5*8x8=320 тактов, для "допаломиноских" AMD получится - 5*25x25=3125 тактов (25=12.5*2), для паломино-торобредо-бартоновских процессоров - 5*48x48=11520 (48=24x2). В результате к концу ресета должна быть достигнута частота FSB/16*koef.

RAMP1. После окончания ресета генератор переключается с деления на 16 на деление на 2. В течение ~0.02ms происходит стабилизация на этой частоте.

RAMP2. После этого генератор переключается с деления на 2 на "полную" частоту. В течение ~0.02ms происходит стабилизация этой частоты.

5. Примерно через 264 тактов выдаётся сигнал SromOE ("Serial ROM Output Enable"). Он даёт разрешение на всю внутреннюю инициализацию процессора (Load SROM, BIST execute etc). В документированных сигналах для AMD таковой отсутствует. Однако присутствие SIP (Serial Initialization Packet) и даже входов для считывания "внешней" Srom у AMD76x может быть достаточным для того, чтоб предположить наличие такового и у AMD (лишь "глубоко" недокументированного). Но даже если такого сигнала и нет – как говорится «смысл остаётся»?

6. Через один цикл (FSB) после снятия ClkFwdRst запускается BIST (внутренний самотест процессора).

7. Ещё через один цикл (FSB) ClkFwdRst снова восстанавливается (BIST продолжается).

8. BIST длится примерно 700 000 тактов. После этого идёт фиксированная пауза (~100 000 тактов) и начинается загрузка SROM в L1-кэш_команд. Загрузка каждой командной "строки" занимает ~50 000 тактов (интерфейс ведь - Serial, как к у модемов).

9. После окончания BIST сигнал TestStat устанавливается в зависимости от его результата: OK - "снимается", Fail - "устанавливается".

У AMD подобный сигнал отстутсвует, но, насколько я понял, он даже в альфе - optional, т.е. лишь для отладки.

10. Второе (и "окончательное") снятие сигнала ClkFwdRst происходит по завершению загрузки SROM. Через 3 цикла (FSB) снимается внутренний ресет и происходит переключение на внешнюю синхронизацию.

11. Процессор уже полностью готов к работе и спустя 264 такта выполняет свою первую микрокоманду по адресу 0x780. Именно по этому адресу были загружены команды SROM, что приводит к выполнению микропрограммы, которая "доинициализирует" "недоинициализированные" <img src="/wink.gif"> после ресета регистры, устанавливает начальные значения и, в конце концов, я так понимаю (это моё ИМХО, т.к. не смог достать подробности SROM - они лишь "для разработчиков"), происходит переход по известному адресу - FFFF:FFF0.

Перечитав всю доступную альфовскую инфу, я даже нашёл структуру SROM и поле для коэффициента, который задаётся аналогичным четырёхбитным кодом. Однако подробности SROM всё ж отсутствуют, да и это (микропрограмма инициализации процессора/шины_EV6, состоящая из микрокодов, загруженная в кэш команд и выполняемая после ресета) именно то, что могло быть изменено в AMD K7.

Что ещё могли изменить в инициализации AMD K7 по сравнению с Alpha 21264? Первое, что приходит на ум: способ засылки SROM в CPU – в альфе он даже имеет специальный тактирующий вход, а в K7 – привязан к частоте SYSCLK. Естественно и микропрограмма другая, но наличие SIP-пакета, думаю, говорит о сохранившемся принципе инициализации – засылка микрокодов в L1-кэш_команд и его выполнение. Не совсем ясен смысл “K7”-сигнала CONNECT (CONNECT is an input from the system used for power management and clock-forward initialization at reset). Видимо, что-то родственное с «альфа»-сигналом SromOE, ведь именно после выставления CONNECT начинается передача SIP (п.6 у K7 и п.5 у альфы). Ну, а про PROCRDY , вообще, не найти чего-то путного, но ясно, что раз он отнесён к AMD_System_BUS-сигналам, значит он точно перекочевал из альфы, может быть, только в несколько изменившейся функциональности.

В общем, сложно предполагать не «располагая»: если у кого-то есть опыт работы с Alpha – большая просьба прокомментировать и высказаться.

Практика

Вышеописанное пока преследовало цель осветить лишь «теоретические» моменты. Теперь же – перейду к «практическим». Главные положения:

FIDы

Они принимают значение от 0000 до 1111 и в случае КУ>12.5 всегда равняются (должны быть такими) 0011:

3210 – бит/ножка/КУ, 0=W1=0.5х, 1=W3=1х, 2=Y1=2х, 3=Y3=4х

0000 – 11х

0001 – 11.5х

0010 – 12х

0011 – >=12.5х

0100 – 5x

0101 - 5.5х

0110 - 6х

0111 - 6.5х

1000 - 7х

1001 - 7.5х

1010 - 8х

1011 - 8.5х

1100 - 9х

1101 - 9.5х

1110 - 10х

1111 - 10.5х

BP_FIDы.

В подавляющем большинстве официальных доков не упоминаются (видел упоминание лишь в доках на самые первые Атлоны), однако играют ПРИНЦИПИАЛЬНУЮ роль, потому как, собственно и задают коэффициент умножения ("начальный" для мобильных – мобильные всегда стартуют с 5х, «номинальный» для них устанавливается БИОСом в процессе POST).

5-битная схема BP_FID (для «допаломиновских» процессоров Athlon Tbird, Duron Spitfire/Morgan, использующих лишь 4-битную схему – см. только младшие четыре), отсортированная по возрастанию коэффициента (по «битам» см. выше про «FIDы»).

43210 - бит/ножка/КУ, 0=AN271=0.5х, 1=AL27=1х, 2=AN25=2х, 3=AL25=4х, 4=AJ27=8х

00100 – 5x

00101 - 5.5х

00110 - 6х

00111 - 6.5х

01000 - 7х

01001 - 7.5х

01010 - 8х

01011 - 8.5х

01100 - 9х

01101 - 9.5х

01110 - 10х

01111 - 10.5х

00000 – 11х

00001 – 11.5х

00010 – 12х

00011 – 12.5х, для Duron – 13х

10100 – 13x

10101 - 13.5х

10110 - 14х

11000 - 15х

11010 - 16х

11011 - 16.5х

11100 - 17х

11101 - 18х

10001 – 19х

10011 – 20х

10111 - 21х

11001 - 22х

11110 - 23х

11111 - 24х

10000 – используется в мобильных процессорах

10010 – используется в мобильных процессорах

Информация была взята из последних биосов, аналогичная была получена многими опытным путём (один из самых популярных источников в этом случае Кандьяк).

В принципе, на этих двух таблицах «практика» и заканчивается. При чём достаточно весело, что кто-то «героически» их получал, перетыкивая десятки процессоров, хотя достаточно было чуть ковырнуть биос – ведь инфу по вычислению КУ биосописатели получают напрямую от AMD. Но это не главное – главное, что они («практические» и «биосные») – совпадают.

Ошибки в схемах

Теперь о проблемах нестарта Tbred со старыми матерями, поддерживающими изменение КУ на примере распространённой Abit-KT7A (VIA KT133A).

После детального анализа работы платы в плане изменения КУ была обнаружена следующая схемотехническая ошибка (точнее – не учёт особенностей «будущих» процессоров). Для считывания «дефаултного» значения КУ используется информация от FID-ов (в «допаломиновсих» процессорах – состояния мостиков L6). Для задания КУ – используется микросхема HCT125 (Quad buffer/line driver; 3-state). Все её входы заземлены и управление происходит посредством сигналов ОЕ, что даёт два варианта на выходе – «0» (земля) или Z-state («бесконечное сопротивление», выход, значит, терминирован на плюс). Наличие лишь двух вариантов (а не трёх – установка «0», «1» и «без влияния на BP_FID») приводит к отсутствию положения “auto” (в биосе его и нет). «Номинальный» же коэффициент устанавливается следующим способом – значение FID попросту «копируется» на BP_FID, т.е. они (FID и BP_FID) по схеме банально соединены (через буферы F244-FID/HCT125-BP_FID). В результате при установленном процессоре с 13x получается:

BP_FID=10100, FID=0011 (т.к. >12.5).

FIDы по схеме копируются на BP_FIDы и на них получается не 10100=13х, а 10011=20х! Естественно, процессору, рассчитанному на 1.7GHz/133FSB, будет сложно завестись на 2.67GHz/133FSB, соответственно, плата просто не запустится.

Можно было бы опустить эту тему как не слишком актуальную – типа, только для процессоров с КУ>12.5, т.е. XP2100+ и выше (а такие не каждый будет ставить на старые матери). Однако, как выяснилось, из-за «интеллектуального» принципа установки FID (процессор их выставляет сам, исходя из значений на BP_FID) возможны многочисленные «неадекватности» - например, выставление на FID 0011 даже при КУ<12.5!.

Эксперименты

Эксперимент с платой Zida PM133 (обычная дешёвая плата, из "самых первых" на KT133, без всякого изменения КУ) + Athlon1700+ (Tbred "B", 11x, разблокирован). При установке этого процессора было обнаружено 0011 на фидах вместо «положенных» 0000. Процессор "совсем" не стартовал (здесь и дальше – всё контролируется POST-картой, соответственно «совсем» обозначает 00 на POST-карте), несмотря на тот факт, что такой же разблокированный XP1700+/11x, только "A"-stepping-а благополучно на ней запускался. Задавшись целью его на ней запустить я посмотрел, как меняются FIDы, при "ручной" установке множителя через BP_FIDы (перемычками на Vcc/Vss). Каково же было моё изумление, когда я выяснил, что процессор стартует ТОЛЬКО в случае, если два младших бита (FID0/1) - единицы (от положения, которое и было на них - 0011=КУ>=12.5)! То для КУ<=12.5 стартует только с четырьмя множителями:

0011 = 12.5х

0111 = 6.5х

1011 = 9.5х

1111 = 10.5х

В случае установки "пятибитного" кода (КУ>12.5, FID4=Vcc) - стартует с любым КУ (который "тянет" проц), ведь для этих КУ "положено" 10011, однако виснет на первых POST-кодах (почему - разбираться было некогда, может и виновен слабый БП, хотя замеченная сильная нестабильность уже на 12.5x путает ситуацию).

Для того, чтобы установить “родной” КУ=11x, пришлось закоротить FIDы на землю (принудительно выставить 0000) плюс подать «0» на BP_FID[4]. Однако даже после всех этих действий не удалось добиться стабильной работы, в то время как на «съедобном» для процессора КУ=10.5х (1111) процессор (и плата – сейчас на них и пишу) работают абсолютно стабильно. Этот эксперимент приведён по следующему поводу. Можно предположить, что «интеллектуальный» принцип выставляемых на FIDы значений (а для стареньких плат плюс то, что они там появляются с некоторой задержкой) может привести к неправильной информации, посылаемой северному мосту, который, в свою очередь, загонит в SIP (в поле коэффициента) неправильную комбинацию и микропрограмма неправильно проинициализирует процессор. Неправильно же проинициализированный процессор, в конце концов, либо будет нестабильно работать, либо совсем не запустится. Просто, если отталкиваться от «возможностей» инициализации микропрограммы из Alpha21264, то ей под силу (точней – она «должна») всё – от банального обнуления регистров до программирования параметров шины EV6 в зависимости от длины дорожек.

В вышеприведённом примере с KT133 сложно увидеть некую зависимость, однако другой опыт показывает как раз её «строгое» наличие.

Схемотехнический просчёт Abit KT7A позволяет изменять значения FIDов без изменения значений на BP_FID (КУ). Для этого был просто взят неразблокированный (вообще - "нетронутый") AMD Athlon 800 (T-brird) и испробованы все варианты установки FIDов (изменялся КУ в биосе, контролируемый реальным напряжением на выходах {2/5/6/9} триггера LS374 - то, что загоняется в NB).

Итак, для Athlon-800+KT133A (неразблокированный 8x, FIDs=1010) было получено:

5x-7x - процессор не стартует совсем

7.5х-11х - всё ОК, но, конечно, из-за «неразблокированности» работает на 8х - 800MHz.

11.5x-12.5x - не стартует совсем

Тайминго-теория

Наличие такой выраженной зависимости может говорить о том, что значение FIDов используется микропрограммой для программирования неких «таймингов» шины EV6. Впервые такое предположение сделал address, получивший похожие результаты с нестартом Tbred-ов на стареньких платах (в первую очередь – KT7A). Им было замечено, что в случае «многоКУшных» процессоров (11х и выше), при попытке их разгона с помощью увеличения КУ, они часто либо не стартуют, либо работают нестабильно. Особенно это было часто при попытках поставить КУ>12.5. В этом случае многие платы с возможностью изменения КУ, не поддерживающие «5-битные» BP_FIDы (КУ>12.5), выставляли на FIDы «стандартную» 4-битовую последовательность (см. выше таблицу FIDов) вместо «положенных» всегда 0011 (при КУ>=12.5). Это чаще всего приводило к нестарту процессора и «лечилось» путём установки КУ=12.5х в биосе (FID=0011) при установке коэффициента «в ручную» – закорачиванием соответствующих BP_FIDов на Vcc/Vss (“принудительно” выставляя таким образом “0” или “1”).

Хоть «тайминго-теория» и имеет некоторые «практические» (и даже «теоретические») основания на жизнь, я не совсем согласен с такой постановкой вопроса – слишком многое она не может объяснить (тот же вышеописанный пример с нестартом Tbred 11x на KT133 – там нет никаких “выраженных” зон). Мне представляется более вероятным «процессорный» источник проблем, т.е. сам процессор «мешает» себе установить коэффициент, он по-разному «ведёт» себя на различных FSB (100/133) и даже зависит от конкретной платы. Например, вышеописанный процессор Tbred 1700, почему-то выставляющий на FIDы 0011, на KT7A выдавал «положенные» 0000 (правда – почему-то не запускался).

Итого

Если кто-то рискнул дочитать до этого абзаца :), подведу итог. Как РАБОТАЕТ установка КУ в AMD K7 - пока не понятно. Для этого надо собрать обширную базу результатов экспериментов (типа вышеприведенных) – и для «старых» и для «новых» плат/чипсетов. А так же, если кто-то может подать/растолковать «теоретические» основы установки КУ (или же указать ошибки в вышеизложенном материале – уверен, они есть) – просьба высказаться. Также хотелось бы заметить, что изменение таблицы соответствия BP_FID и FID с множителем может являться объяснением механизма блокировки множителя AthlonXP. Это косвенно подтверждается поведением при выставлении множителя вручную - либо игнорирование установки, либо нестарт системы (гораздо чаще второе). Стоит проверить на штатном множителе камень и соотнести с таблицой, приведённой apple_rom.

Попытка разобраться с механизмом выставления множителя на SocketA, а также рассмотрение и развенчание наиболее распространённых мифов и заблуждений была осуществлена в этой статье.

В любом случае – имеющие возможность пару раз тыкнуть напряжометром – не поленитесь это сделать с вашим процессором/платой, особенно в случае «загадочного» нестарта и близких к вышеперечисленным проблемам.

п.с. Убедительная просьба - не кидать сюда постинги с вопросами «а как мне поставить такой-то КУ на такой-то плате/процесоре» – для этого создано немало веток в том же «Разгоне и Охлаждении».

Отправить комментарий